More Information About CMOS IPs

The following provides more information about each of the CMOS IPs.

ADC: 10b, 10MS/sec, 1V, 10µW, compact size (0.003mm2)

This is a differential SAR ADC with a sampling rate of 10MS/s, ENOB of 8b, SNDR of 50dB, and 10uW power consumption. A separate ip block is available to facilitate the ADC clocking with a single clk and on/off signals. The ADC is robust against the comparator offset non-linearities and is equipped with comparator offset calibration. The compact form factor and power efficient behavior of this ADC makes it a good candidate for control and tuning applications.

OpAmp: 1V, 60dB gain, 1MHz

The OpAmp is differential to single-ended. The OpAmp is suitable for general purpose applications including signal amplification, LDO, filtering.

TIA: 1V, 500KHz, 6b linearity

The TIA has a transimpedance gain of 5kΩ, and it is suitable for monitoring and tuning applications.

Comparator: 100MHz, 1V, 100nW, offset <2mV with offset calibration

A low-power comparator with background offset cancellation.

Low-offset Comparator

A comparator with an input referred offset voltage of 2mV. This comparator does not require calibration.

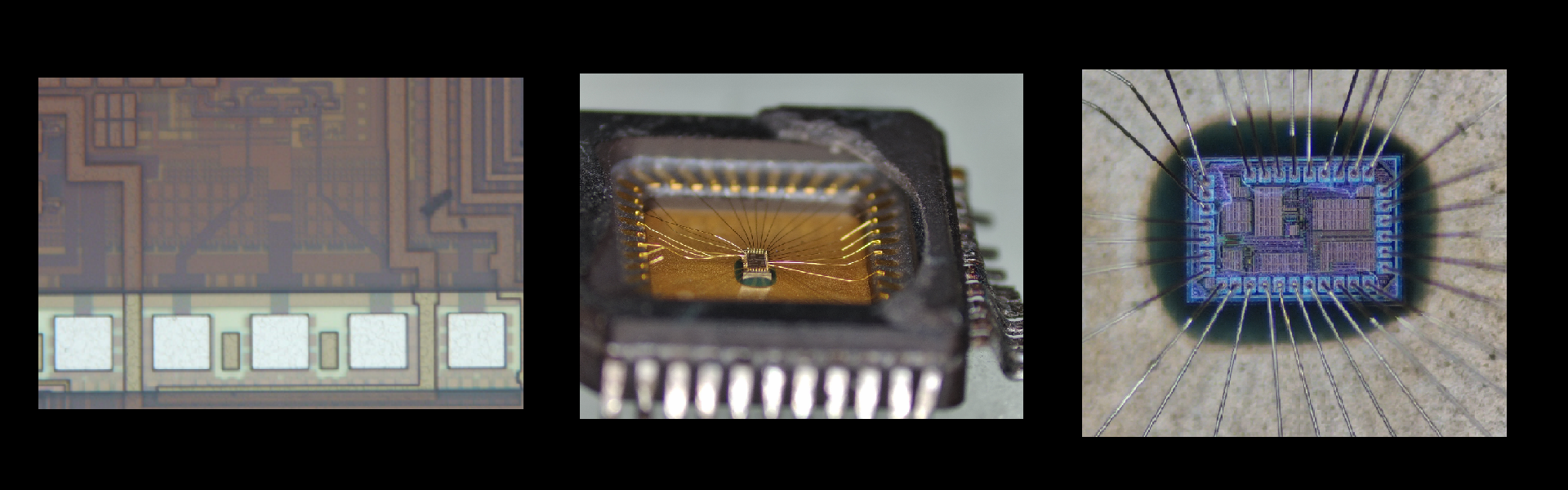

PADs and ESD circuits: 1V, 3.3V

1V and 3.3V Analog and Digital PADs are available. We also provide 1V PADs with low capacitance suitable for RF applications.

Area Saving PADs (1V) with clk or I/O buffers

These pads have built-in digital I/O buffers with pull up/down resistors under the pad to minimize the pad area. A 50Ω clock PAD is also available.

Scan chain: 1V, 10b continuous time 500Mbs

A fast scan chain is available for control and calibration purposes. Only the clk and data pads are required to communicate with the chip.

Reconfigurable counter: 1V, 16b, 1GHz

This digital counter could be easily configured (by adding a single metal polygon to the layout) for counting applications.

Digital I/O buffers: 1V, 3.3V

These 1V and 3.3V digital I/O buffers are capable of driving a 50pF load at 50MHz.

Bandgap: 1.1V ±30mV in 0°C to 90°C

The 1.1V Bandgap offers a robust reference voltage in a wide temperature range. The Band gap could be used in an LDO or as a reference to build an accurate on-chip current reference.

PoR: 1V, 1µs PW, 10µs delay

POR generates the reset signal right after powering up the chip eliminating the need for an external reset signal.

Maturity level

The following table describes the maturity level of the CMOS IP.

| Maturity Level | Description |

| Bronze | Simulation proven IPs. These IPs may not be ready for tapeout, and they may have DRC Issues. |

| Silver | Tapeout ready IPs. These IPs have been thoroughly tested and prepared for high yield. Some of these have been taped out but not measured yet. |

| Gold | ≥1 tapeout, >5 dies successfully measured |

| Platinum | ≥2 tapeouts, >10 dies in each run successfully measured |

Category type

The following table describes the category type of the CMOS IP.

| Category Type | Full Name | Description |

| A | Basic Analog | A package of general purpose analog IPs. The full package will be provided as a bundle. |

| D | Basic Digital | A package of general purpose digital IPs. The full package will be provided as a bundle. |

| SI | Single IP | One IP or a group of IPs with a specific application and specs. Each IP in this category is acquired by the customer separately. |

| CI | Custom IP | An IP with a specific application whose specs can be tuned to the customer needs. Each IP is acquired by the customer separately |